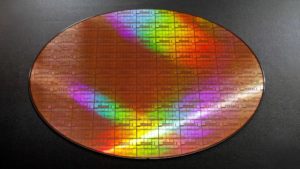

隨著英特爾新一代處理器 Panther Lake 進入量產準備階段,市場近期流出更多關於 Intel 18A 製程的設計細節,包括金屬層配置、GAA pitch 參數,以及背面供電(PowerVia)在不同電路區塊的實作方式。相關資訊顯示,Panther Lake 採用全 HP cell 設計,M0 金屬層最小 pitch 為 36nm,而 SRAM 並未導入 PowerVia 架構。 繼續閱讀..

英特爾 18A 更多技術細節曝光,Panther Lake 架構逐步明朗 |

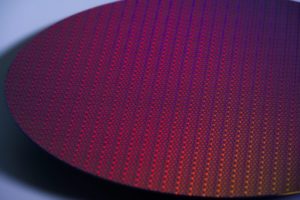

| 作者 蘇 子芸|發布日期 2026 年 02 月 23 日 14:48 | 分類 IC 設計 , 半導體 , 晶圓 |